D Flip Flop:

D flip-flops are used in memory storage components and also in data processors. D flip-flops can be made using either a NAND or a NOR gate. Due to their flexibility, they are available as IC packages. When the clock signal is LOW, the input has no effect on the output state.

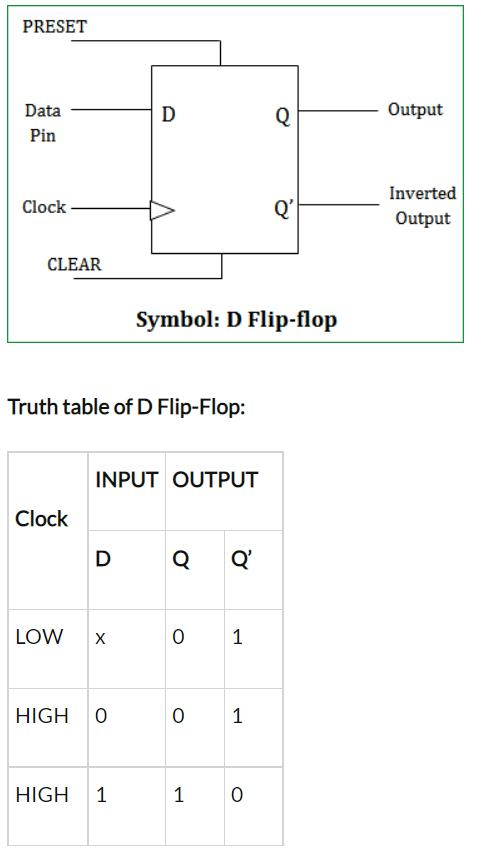

The clock must be set high for the inputs to be active. As a result, flip-flop D is a controlled bistable latch, with a clock signal as the control signal. This is once again divided into positive edge-triggered D flip-flops and negative edge-triggered D flip-flops. As a result of the inputs below, the output has two stable states.

D(Data) is the state of the D flip-input flop. Q and Q' reflect the states of the flip-output flop. According to the table, the output changes its state depending on the inputs. The crucial thing to remember is that all this can only happen in the presence of a clock signal. For auxiliary inputs only, it works exactly like an SR flip-flop.